## Handwritten Notes **Digital Electronics**

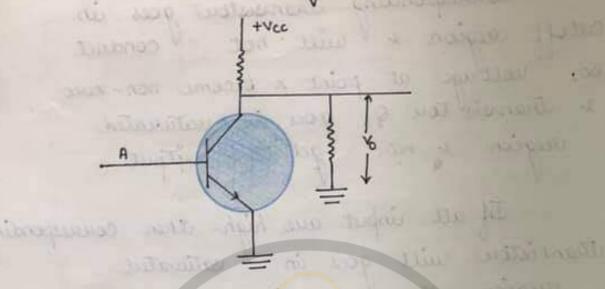

HEARTH & THESE THE STATE OF THE STATE OF If unput A is in clow estate other tuans istou goes in cutoff vugion 2 me get high output if unput is in high state then their sistem goes in saturated region & me get now editput

NOT Gate work as Investore

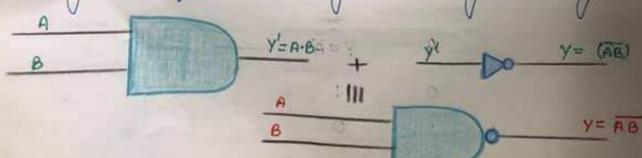

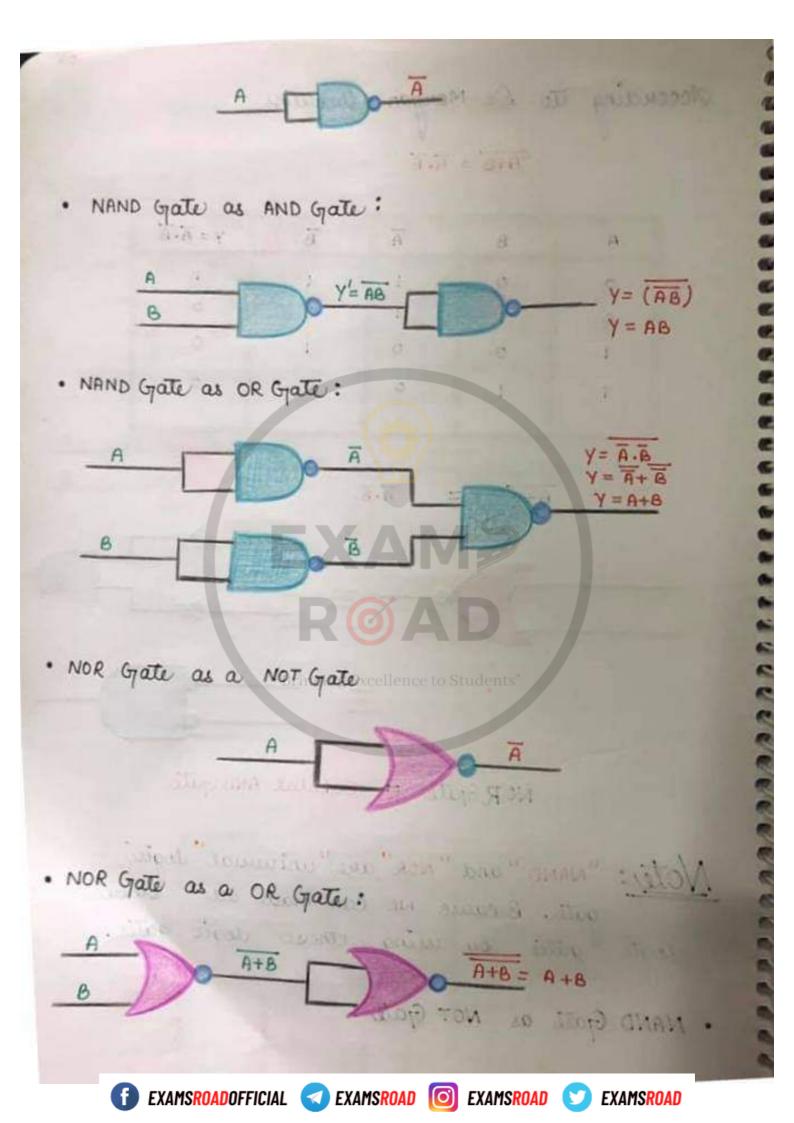

#### NAND Gate:

COMPANDE AND THE SE NAND Gate is a combination of NOT - AND gate. It has two on more in put 2 only single output. so, degic symbol for NAND gate is given by

the field on the factor medicine

### NAND Gate = Bubbled OR Gate : MANT ATTEM

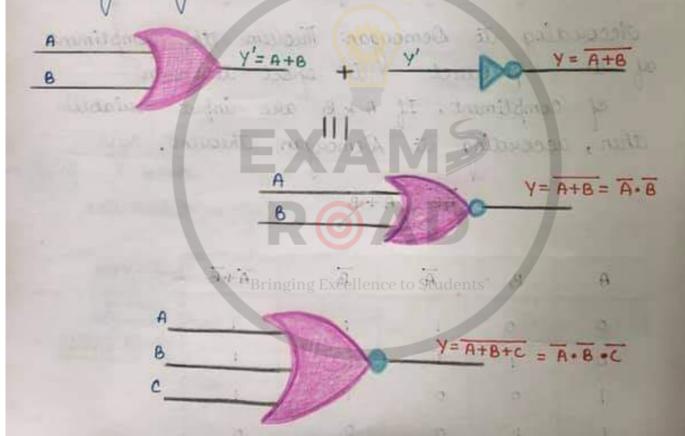

NOR Gate:

NOR gate is a combination of NOT-OR gate it has the on more input but have only using le output if A & B ave input varioable other clogic symbol can be expuess as;

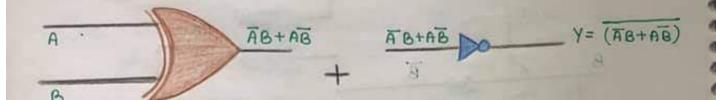

#### Trath Table:

| 0   | 1 |     |         |  |

|-----|---|-----|---------|--|

| n   | В | A+B | Y = A+B |  |

| 0   | 0 | 0   |         |  |

| 0   | 1 | 1-1 |         |  |

| - 1 | 0 | 1   | 0       |  |

| 1   | 1 |     | 0       |  |

|     |   | 4   | 0       |  |

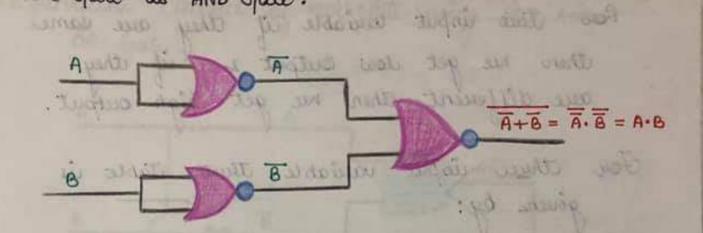

NOR Gate as AND Gate:

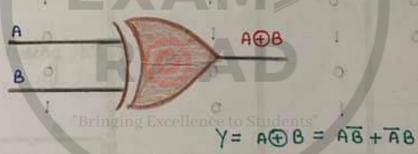

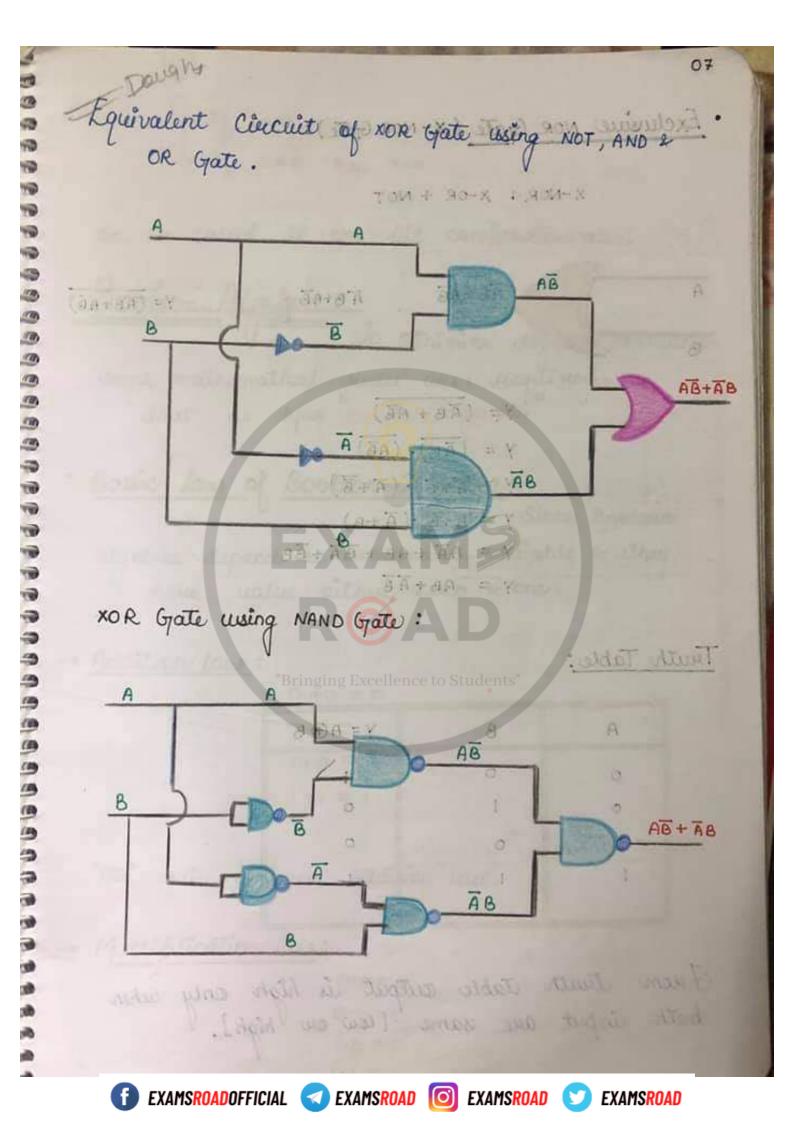

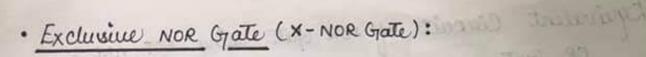

XOR Gate (Exclusive - OR Gate): (7th february 2019) (Thursday)

A xor gate have

the on more input but have only single output, the logic symbol for xor gate is given by;

Truth Table: you to make the short suntano all

10

| AA (a+ 1) | B. 7848 | Y=A+B |

|-----------|---------|-------|

| 30 A 34   | 0       | 0     |

| ABO BA 7  | P       | 1     |

| p: 38 = 7 | 8€      | 1     |

| 1 70      | YEAR!   | 0     |

Fou two input vaniable if they are same then we get low output & if they are different then we get high output.

For these input variable touth table is given by:

| A | В       | С        | A⊕B                  | A⊕B⊕C AOX         |

|---|---------|----------|----------------------|-------------------|

| 0 | et o to | 0        | 0                    | 0                 |

| 0 | 0       | 1 per 14 | and o'and au         | The cue ment dish |

| 0 | 1 30    | 0        | bodsday 500          | all total         |

| 0 | 1       | 1        | : 1                  | C 0 2200          |

| 1 | 0       | 0        | XAM                  |                   |

| 1 | 0       | 1 34     |                      | 0 4               |

| 1 | 1       | 0        | K (6) A 1            |                   |

| ľ | 074     | Bring    | ng Excellence to Stu | dents"            |

The another logic expression of xor gate

$$Y = A \oplus B = A \overline{B} + B \overline{A} = (A + B) \overline{A} \overline{B}$$

$$= (A + B) (\overline{A} + \overline{B})$$

$$= A \overline{A} + A \overline{G} + B \overline{A} + B \overline{B}$$

$$\Rightarrow A \overline{A} = B \overline{B} = 0$$

$$Y = A \overline{B} + B \overline{A}$$

$$y = (\overline{A}B + A\overline{B})$$

$$y = (\overline{A}B) \cdot (\overline{A}B)$$

$$y = (\overline{A} + \overline{B}) \cdot (\overline{A} + \overline{B})$$

$$y = (A + \overline{B}) \cdot (\overline{A} + B)$$

$$y = (A + \overline{B}) \cdot (\overline{A} + B)$$

$$y = A\overline{A} + AB + \overline{B}\overline{A} + \overline{B}B$$

$$y = AB + \overline{A}B$$

Chaing MAND Grate

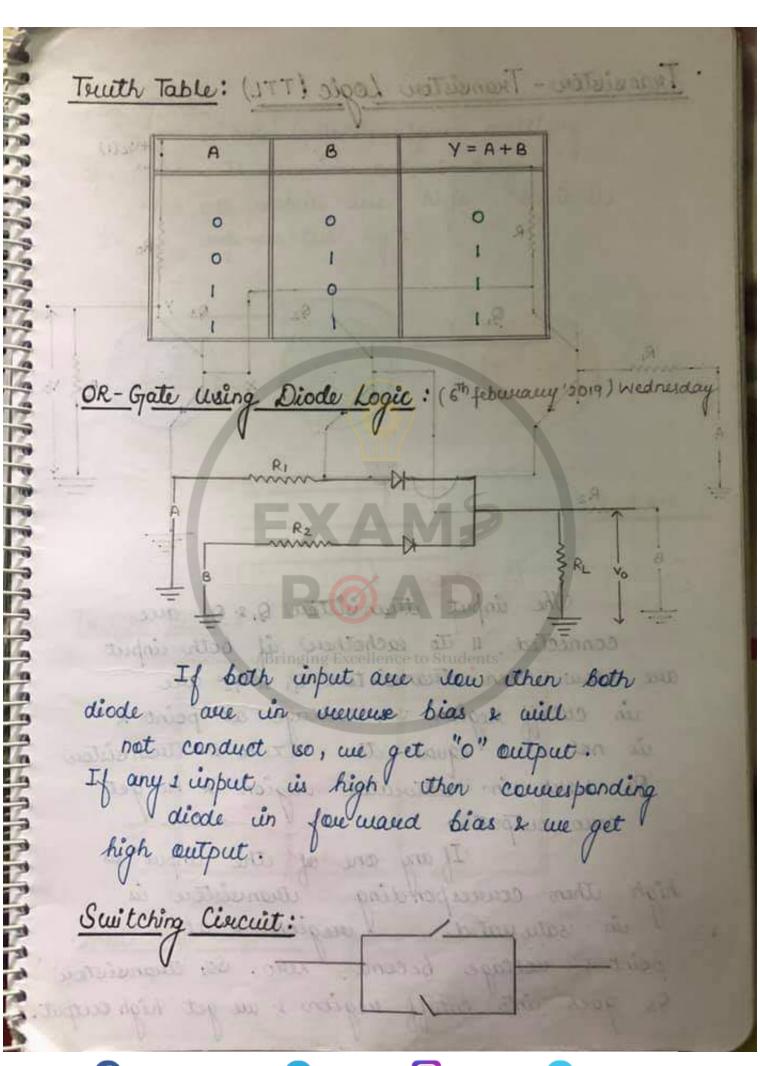

#### Truth Table:

14

| А | Bringing Exe | Y= A⊕B |

|---|--------------|--------|

| 0 | 0            | 1      |

| 0 |              | 0      |

| 1 | 0            | 0      |

| 1 | 1<br>8 A     | 1 8    |

From twith table output is high only when both input we same [ now on high].

If

$$A=B$$

then  $Y=1$  then  $Y=0$

180, we called it one bit comparation also.

# Boolean Algebra: To minimize Mogical expression

some mathematical vules are regulised, that is Klas Boolean Algebra.

## Basic Law of Boolean Algebra: Since Boolean

algebra depend on arthematic variable & they have value either zero & one.

#### Communication claus lead held and the → Addition Law:

- Association Property: 'OR' Gate penfour Addition Law.

#### the admition & multiplication -> Muttiplication Law:

and my terptication days.

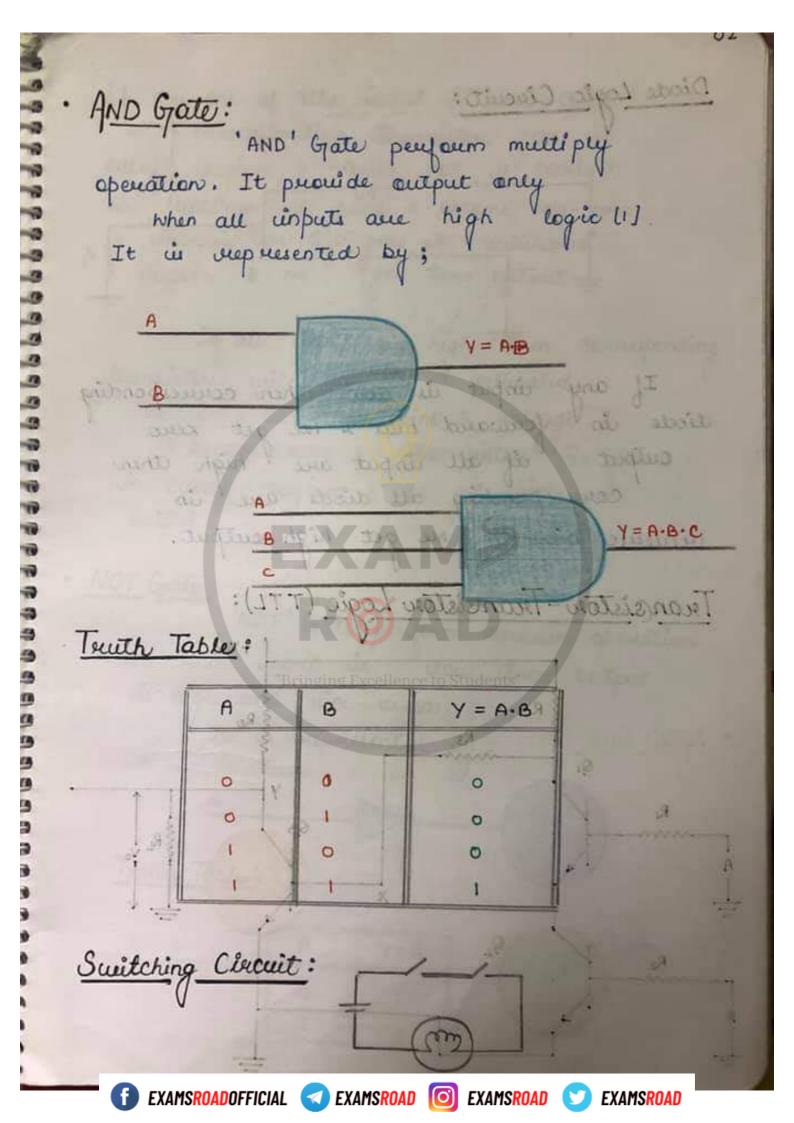

Logic Gate have many input but only one output. We can penjour authematic operation by using Logic Gate Circuit. Example: AND, OR, NOT, NAND, NOR, X-OR, X-NOR .. · OR-Gate: OR-Gate have thus on more input but have only one output. The output of OR-Gate Vies high when any one of unput is high. If A&B are input variable of or gate then, output Y is our resented by; A Y= A+ B+C Bringing Excellence to Students "OR" Gate peufour Plus (+) operation.

180, Boolean Multiplication is same as AND operation.

Properties of Boolean Algebra:

a Mathematical system which consist two or more I raviable and depend on two operation which is denoted by OR(+) and AND(.).

Property:

Basic Low of Becken Mashen!

Commutative Pooperty:

Boolean Algebra fellow

commutative law fou both addition and Multiplication daw.

A+B = B+A

A.B = B.A

→ Associative Property:

The associative property

for addition & multiplication is

given by (A+B)+C = A+(B+C)

(A+B)+C = A+ (B+C)

] == [++i

(A-B). C = A. (B.C)

→ Distributive Property:

The Boolean Addition

despotent lane:

1 = 14-0

1=7+0

I: Tomila

is distributive over Boolean multiplication which is given by and noise and added

$$A + BC = (A + B) (A + C)$$

=  $A \cdot A + A \cdot C + B \cdot A + B \cdot C$

- Absorption Law: 10 mount of

· A + AB = A(1+B) = A cellence to Students"

· A+AB = (A+A)(A+B) ( +B) and to product a (8+A) onto lineral

al A P B. · A(A+B) = AA + AB = A+ AB = A(1+B)= A

· A(A+B) = AA+AB Compliance of preduce A & A & A combliment of A & B.

15555EV

**★ EXAMSROADOFFICIAL ★ EXAMSROAD ★ EXAM**

→ Idempotent Law: : Total of the state of t

A+A=A, A·A=A

is distribution could becker multiplication

→ Double Invension Law:

A HA DEAL HOUSE

Do Bor the work of a stand of

OR operation AND operation

A+0 = A

28 + 24 + 12+ A.0 = 0

A+1=1

A-1= A

A+ A=1

A-A=O

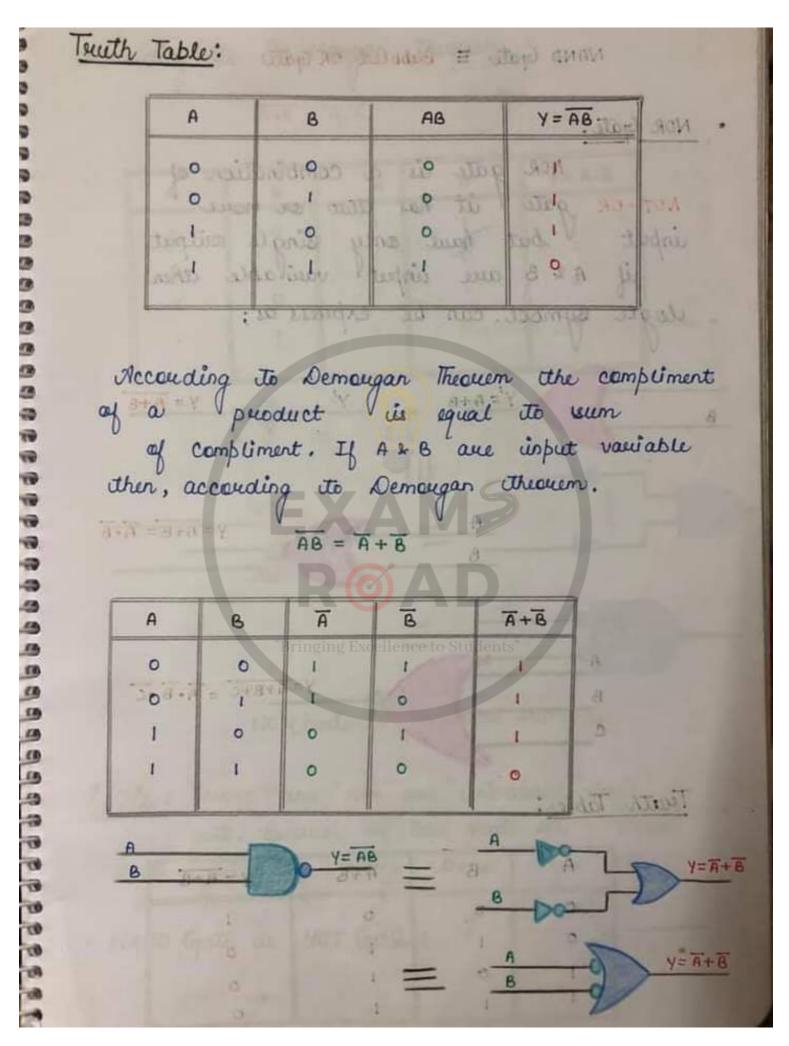

<u>De-Morgan Theorem:</u>

De Morgan has ituo statement. 1017 0000 "

38 (8±1)-A =

Statement: I

"Bringing Excellence to Students" Compliment of the sum of A & B is equal its the product of compliment Of A & B. 36 + 66 = (8+6) A .

A+8 = A . B . . . . .

Statement: I

compliment of purduct of A & B is equal its the sum of compliment of A & B.

80+A0 = (8+A A .

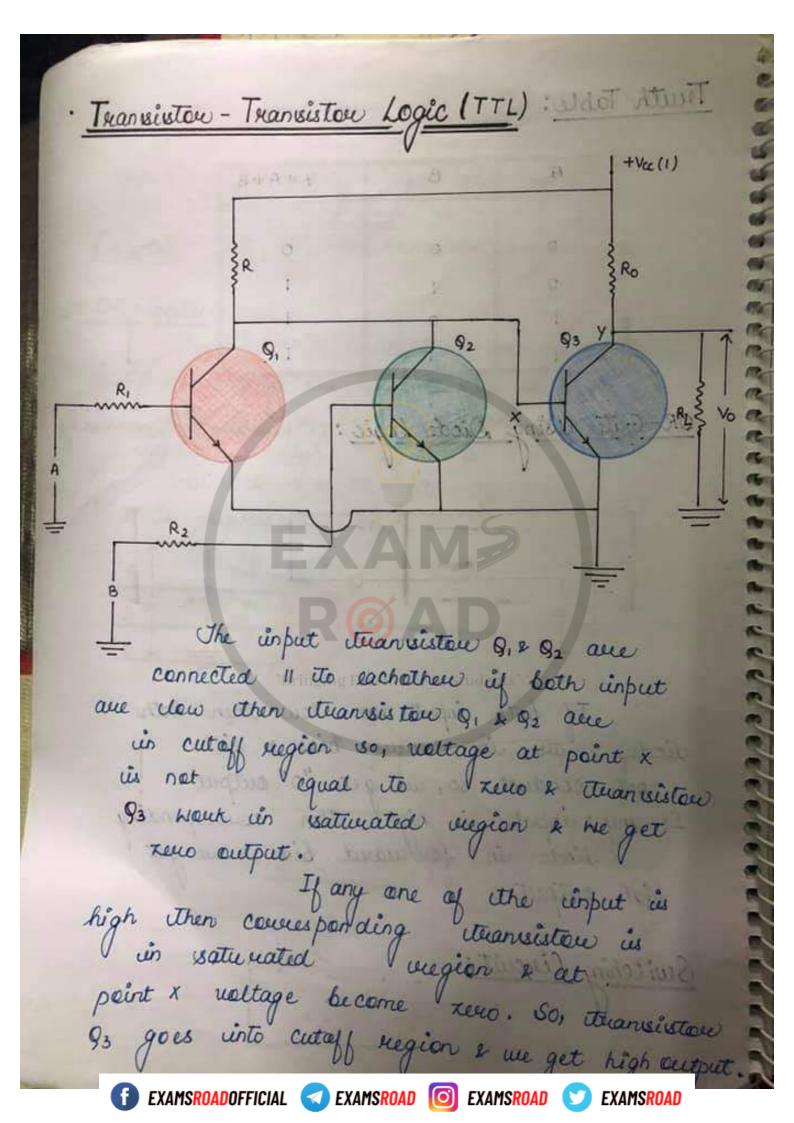

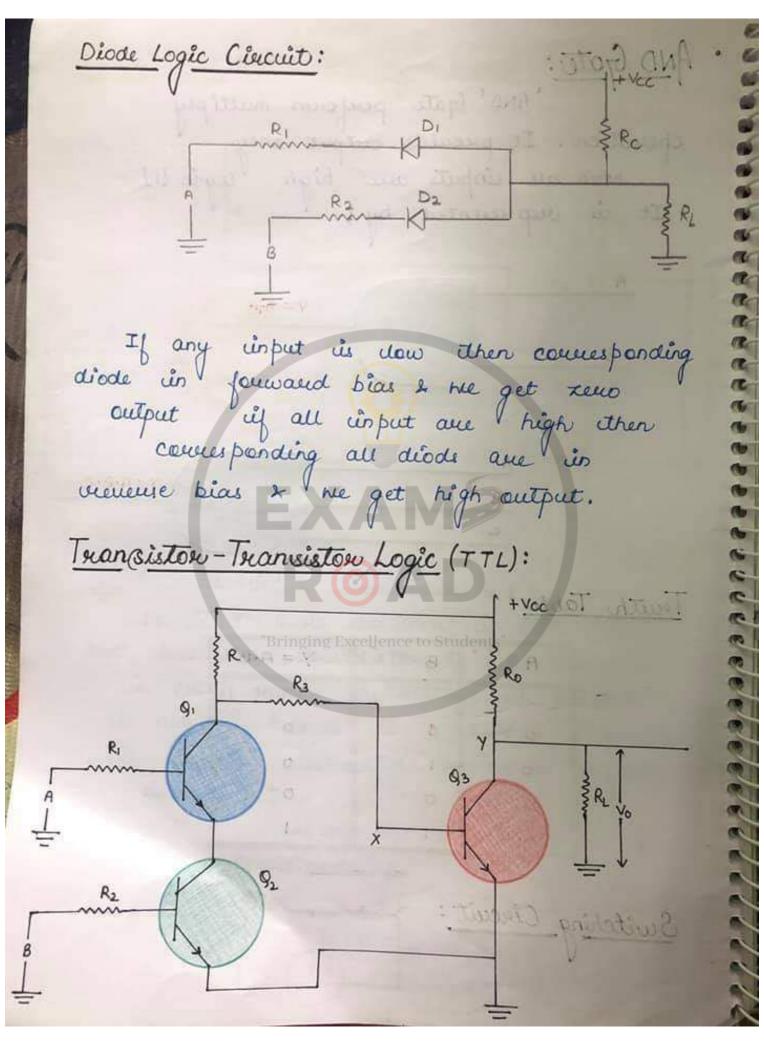

If any one of the surplist as down aheat would conversionaling transister goes in cutoff vegion e will not conduct 180, haltage at point x become non-xero 2 transis tou 93 goes in saturated uegion 2 ne get zero output. If all input are high then coversponding iteraristen will goes in saturated vegion. so, at point x veltage become xeux & ituansistem 80 goes output. sole and window L 'NOT' Gate peufour vieneuse operation means when input is now then output is high and wice- we was. It is supresented by; : Top QUAN. An is suit of the year in - Tour input & only wingle cultput, so, seal Touth Table: SA SEV

| A | y = An-A |  |

|---|----------|--|

| 0 | 1        |  |

| 1 | 0        |  |

DATY